# Multi-stacked silicon wire waveguides and couplers toward 3D optical interconnects

J. Kang\*<sup>a</sup>, N. Nishiyama<sup>a</sup>, Y. Atsumi<sup>a</sup>, T. Amemiya<sup>b</sup>, and S. Arai<sup>a,b</sup>

<sup>a</sup>Dept. of Electrical and Electronic Engineering, <sup>b</sup>Quantum Nanoelectronics Research Center,

Tokyo Institute of Technology, Tokyo, Japan

# **ABSTRACT**

The relationship between the propagation loss and roughness on multi-layered Si waveguides fabricated up to a  $3^{rd}$  layer was investigated. By reducing the surface and sidewall roughness of the waveguides, a low propagation loss of 3.7 dB/cm for the 3 layer a-Si:H waveguides was demonstrated. Furthermore, vertical coupling between multilayer waveguides was demonstrated by use of a grating-type vertical coupler. A coupling efficiency of 22% was obtained for 10 pairs of gratings with a period of 640 nm, even with a layer distance of 1 $\mu$ m.

Keywords: Si photonics, multilayer waveguide, amorphous silicon, propagation loss, vertical coupling, grating coupler

# 1. INTRODUCTION

Conventional electrical connections are facing difficulties with regards to signal transmission, even at on-chip data links, due to continued miniaturization of devices. This continued miniaturization, otherwise referred to as the "scaling law", results in an increase of the transmission delay of electrical interconnects within an LSI chip, thus limiting the transmission speed (to ensure signal quality). Silicon photonics is one of the key technologies currently being developed to overcome the speed limitation of electrical interconnects in LSIs<sup>1,2</sup>. Up to now, comparisons between optical and electrical interconnects have been drawn and the device requirements for optical interconnects have been predicted<sup>3,4</sup>. Many types of actual optical components in the silicon-on-insulator (SOI) platform have already been demonstrated<sup>5-8</sup> as well as the integration of photonic and electronic circuits<sup>9,10</sup>. Integration density has gradually increased and a transmission density of 6.6 Tbps/cm<sup>2</sup> was demonstrated with optical interconnects integrating arrayed laser diodes, silicon optical modulators, and germanium photodetectors on a single SOI substrate<sup>11</sup>.

The above mentioned Si photonic devices were mainly fabricated with crystalline silicon (c-Si). In such a process, the photonic devices are made before, or at the same time as the complementary metal oxide semiconductor (CMOS) fabrication: the so-called "front-end process". For such a front-end process, however, we have to change the design rules of the CMOS logic layer in order to introduce optical circuits. For this reason, it may be preferable to fabricate photonic circuits after the CMOS logic layer fabrication method: the so-called "back-end process". Hydrogenated amorphous silicon (a-Si:H) and SiN are core materials of Si photonics with CMOS back-end process compatibility and low-temperature fabrication <sup>12,13</sup>. In particular, a-Si:H has the advantage of a high refractive index that is essential for nanophotonic devices.

Until the early 2000s, many research groups studied the deposition conditions of a-Si:H films<sup>14,15</sup>. Amorphous silicon tends to have high optical absorption due to dangling bonds present in the film that can be terminated with H atoms resolved from a silane (SiH<sub>4</sub>) precursor gas during the deposition process. Such a treatment results in low defect densities and in addition, a slight dilution of SiH<sub>4</sub> with Ar can lead to an increase of terminated dangling bonds, lowering the compressive stress of the a-Si:H film thus making it more mechanically stable <sup>16</sup>.

Multi-stacked optical layers can provide higher integration density as well as increased total bandwidth without damage to the CMOS logic layer. Moreover, there is an additional benefit that multilayer stacking can reduce the optical crosstalk at waveguide crossings, which leads to reduction of total loss<sup>17</sup>. If we utilize the low loss a-Si:H film in optical circuits, multi-layered optical circuits consisting of a-Si:H and SiO<sub>2</sub> layers can be realized. Unique structures such as vertically slotted waveguides, or multi-layered waveguides combined with several kinds of cladding materials (optimized for each layer), can also be realized.

Optoelectronic Interconnects XIII, edited by Alexei L. Glebov, Ray T. Chen, Proc. of SPIE Vol. 8630, 863008 · © 2013 SPIE · CCC code: 0277-786/13/\$18 · doi: 10.1117/12.2009456

Proc. of SPIE Vol. 8630 863008-1

Here we present two important elements for the realization of three-dimensional (3D) optical circuits as well as multi-stacked layers. First, the mechanism of optical-loss at multilayer waveguides will be revealed  $^{18}$ . In Section 2 the relationship between the propagation loss and roughness of the multilayer waveguides will be discussed both theoretically and experimentally. Secondly, the vertical coupling system between multilayer waveguides will be discussed. In order to couple light without concern for optical isolation between vertically-stacked waveguides, we introduced gratings with a layer-to-layer distance of 1  $\mu$ m to assist vertical coupling. In Section 3 the simulation and measurement of the layer-to-layer grating coupler will be discussed.

# 2. MULTI-STACKED WAVEGUIDES AND THEIR CHARACTERISTICS

#### 2.1 Deposition conditions of the a-Si:H film

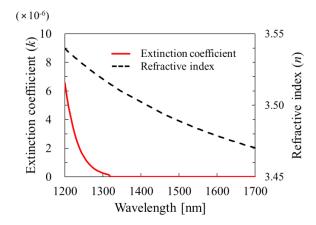

The a-Si:H layers were deposited by plasma-enhanced chemical-vapor-deposition (PECVD) on a SOI substrate. The SOI substrate consisted of a 3  $\mu$ m thick buried oxide (BOX) layer and a 220 nm thick c-Si layer. To check the deposition conditions were satisfactory we measured the extinction coefficient and refractive index of a deposited a-Si:H film by the ordinary ellipsometry method. The deposition conditions were as follows: SiH<sub>4</sub> flow rate = 100 sccm; Ar flow rate = 100 sccm; power = 100 W; pressure = 130 Pa; and temperature = 300 °C. This corresponded to a deposition rate of 2.2 nm/sec.

Figure 1. Wavelength dependence of the refractive index and extinction coefficient for the a-Si:H film.

Figure 1 shows the wavelength dependence of the refractive index and extinction coefficient. The refractive index was 3.48 at a wavelength of 1.55  $\mu$ m and the measured extinction coefficient was below the measurement limit (<1.5×10<sup>-7</sup>) of the system (corresponding to an optical absorption of  $\alpha$ <0.01 cm<sup>-1</sup>). This ellipsometry measurement indicates that the material loss of our deposited a-Si:H film was negligible for waveguides.

# 2.2 Surface roughness of the multi-stacked a-Si:H film

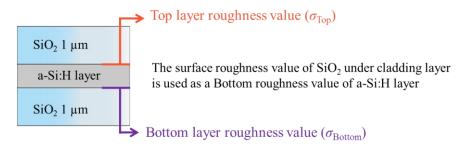

Although, as mentioned above, the material loss can be negligible, there is another important loss mechanism present in the multi-layered a-Si:H film: scattering loss due to surface roughness. Degradation of the surface roughness could become a serious concern in the case of multi-stacking of a-Si:H waveguides. As illustrated in Fig. 2, a 1  $\mu$ m thick SiO<sub>2</sub> layer was deposited between each a-Si:H layer to act as cladding.  $\sigma_{\text{bottom}}$  refers to the surface roughness before a-Si:H deposition (in other words, the roughness of the top of the SiO<sub>2</sub> film) and  $\sigma_{\text{top}}$  refers to the roughness values after the deposition of the a-Si:H film. The surface roughness determined before and after the deposition of a 220 nm a-Si:H layer was measured by atomic force microscopy (AFM) and is listed in Table 1 as root-mean-square (RMS) values. As you can see from Table 1, the top surface roughness of the a-Si:H film was inferior to that of the c-Si film. A surface roughness of over 5 times the  $\sigma_{\text{top}}$  value for the 1<sup>st</sup> layer of c-Si was obtained at the 2<sup>nd</sup> and 3<sup>rd</sup> layers of a-Si:H (1.06 nm and 1.03 nm, respectively).

Figure 2. The surface roughness measurement ( $\sigma_{top}$  and  $\sigma_{bottom}$ ).

Table 1. The measured (RMS) surface roughness of each layer.

| Measured point                                     | 1 <sup>st</sup> layer | 2 <sup>nd</sup> layer |       | 3 <sup>rd</sup> layer |       |

|----------------------------------------------------|-----------------------|-----------------------|-------|-----------------------|-------|

| Deposition pressure                                | c-Si                  | 130 Pa                | 30 Pa | 130 Pa                | 30 Pa |

| $\sigma_{\mathrm{top}} \left( \mathrm{nm} \right)$ | 0.17                  | 1.06                  | 0.30  | 1.03                  | 0.52  |

| $\sigma_{ m bottom}$ (nm)                          | (0.18)*               | 0.24                  | 0.24  | 0.37                  | 0.36  |

<sup>\*</sup>  $\sigma_{\text{bottom}}$  of the 1<sup>st</sup> layer of c-Si was measured after etching the c-Si film.

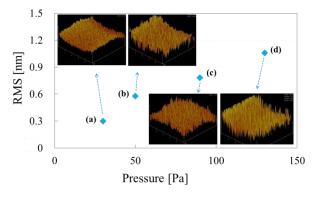

In order to improve the surface roughness, we lowered the deposition pressure of the a-Si:H film from 130 Pa to 30 Pa, thus enhancing the migration of atoms. Table 1 also lists the RMS surface roughness for the a-Si:H films under deposition pressures of 30 Pa. As the deposition pressure decreased, the surface roughness reduced from 1.06 nm (at 130 Pa) to 0.30 nm (at 30 Pa). This can be attributed to an increase in the migration length of the atoms at lower deposition pressures, which led to a lower deposition rate of 0.3 nm/sec at 30 Pa. The surface roughness  $\sigma_{top}$ , as well as the corresponding AFM image is shown in Fig. 3 as a function of the deposition pressure.

Figure 3. AFM measurements of the surface roughness of the a-Si:H film as a function of deposition pressure: (a) 30 Pa, (b) 50 Pa, (c) 90 Pa, and (d) 130 Pa.

# 2.3 Sidewall roughness of the a-Si:H waveguides

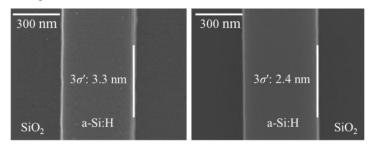

Previous experiments have focused on the surface roughness of multilayer a-Si:H films. However, the sidewall roughness is also a potential issue with respect to the loss property of waveguides. Waveguides presented here were patterned by electron beam (EB) lithography with a double-layered ZEP resist<sup>19</sup>. In this study, 2 types of dry etching - conventional reactive-ion-etching (RIE) and inductively-coupled-plasma (ICP) RIE - were used. The advantage of ICP-RIE is that a low processing pressure can be applied that assists the directionality of the ion flux in the chamber leading

to better vertical shapes during the etching process<sup>20</sup>. The width of the Si waveguides was 450 nm for the RIE etched waveguides and 500 nm for the ICP-RIE etched waveguides, both of which are shown in the scanning electron microscope (SEM) images of Fig. 4.

Figure 4. Top-side SEM images of the a-Si:H waveguides formed by RIE (left) and ICP-RIE (right).

From the SEM images of Fig. 4, the sidewall roughness values  $(3\sigma')$  of the waveguides after RIE and ICP-RIE were measured as 3.3 nm and 2.4 nm, respectively. Furthermore, the sidewall angles of each waveguide were determined to be  $81^{\circ}$  and  $85^{\circ}$ , respectively.

# 2.4 Propagation loss of the multilayer waveguides

A selection of multilayer a-Si:H waveguides fabricated under deposition pressures of 30 Pa and 130 Pa, and RIE and ICP-RIE etching were studied. As the light source for the propagation loss measurements, transverse-electric (TE) polarized light from a tunable laser emitting in the C-band (1.55  $\mu$ m) was coupled to both edges of the waveguides through tip-lensed single-mode fibers. The propagation losses were then calculated using the cutback method.

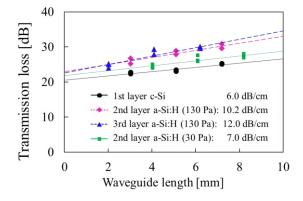

Figure 5 shows the result of measured losses against the propagation length of the RIE-etched waveguides. For a deposition pressure of 130 Pa, the propagation losses of the  $1^{st}$  c-Si layer (circles), the  $2^{nd}$  and  $3^{rd}$  a-Si:H layers (diamonds and triangles, respectively), were 6.0 dB/cm, 10.2 dB/cm, and 12.0 dB/cm, respectively. In contrast, the propagation loss of the  $2^{nd}$  layer of a-Si:H with a deposition pressure of 30 Pa (squares) was 7.0 dB/cm; a reduction from 10.2 dB/cm to 7.0 dB/cm by simply reducing the deposition pressure. This improvement in the scattering loss from the surface can be attributed to an improved surface roughness.

Figure 5. Measured losses against the propagation length of the RIE-etched waveguides.

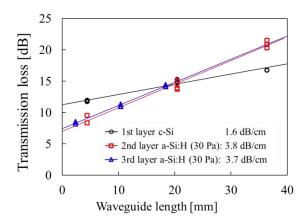

Figure 6. Measured losses against the propagation length of ICP-RIE-etched waveguides.

For the waveguides formed by ICP-RIE etching, a deposition pressure of 30 Pa was used for the a-Si:H film. Fig. 6 shows the corresponding propagation loss of the waveguides formed by ICP-RIE where a loss of 1.6 dB/cm, 3.8 dB/cm, and 3.7 dB/cm was measured for the 1<sup>st</sup> layer of c-Si (circles), 2<sup>nd</sup> layer of a-Si:H (squares), and the 3<sup>rd</sup> layer of a-Si:H (triangles), respectively. Although the width of the ICP-RIE etched waveguides was wider than that of the RIE etched waveguides, the contribution towards loss was as low as 0.1 dB/cm; an additional 3–4 dB/cm improvement was obtained mainly due to a reduced sidewall roughness (from  $3\sigma' = 3.3$  nm to 2.4 nm). The coupling efficiencies (the loss at the 0 mm) were different from the results of the RIE etched waveguides shown in Fig. 4. This is because a spot-size converter was introduced that was comprised of narrow waveguides (240 nm wide for a-Si:H waveguides and 280 nm wide for the c-Si waveguides) with a tapered structure in order to improve the coupling efficiency<sup>21</sup>. This difference did not, however, affect the propagation loss.

The scattering loss due to surface roughness can be expressed as follows:

$$\alpha_{surface} = B^2 \left(\frac{\cos^3 \theta}{2\sin \theta}\right) \left(\frac{1}{h + \frac{1}{p} + \frac{1}{q}}\right) \tag{1}$$

$$B = \left(\frac{4\pi}{\lambda}\right) \left(\sigma_{top}^2 + \sigma_{bottom}^2\right)^{\frac{1}{2}} \tag{2}$$

where,  $\theta$  is the angle of propagation of rays in the waveguide; 1/p and 1/q, are the penetration depths of the mode into the cladding; and h is the waveguide thickness.

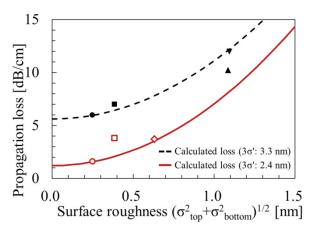

Fig. 7 shows the measured propagation losses plotted against the RMS values of the surface roughness expressed as  $(\sigma_{top}^2 + \sigma_{bottom}^2)^{1/2}$ . The calculated losses after consideration of surface roughness and sidewall roughness (dashed black line and solid red line) are also shown<sup>22,23</sup>, where the values for  $\theta$ , p and q were calculated by the finite difference method. The sidewall roughness was assumed to be 3.3 nm and 2.4 nm (3 $\sigma$ ' values) for the waveguides prepared by RIE and ICP-RIE, respectively. The scattering loss at the sidewall was assumed to be 5.6 dB/cm and 1.2 dB/cm for the RIE and ICP-RIE prepared waveguides, respectively.

The measured propagation losses agreed well with calculations, indicating that the primary cause of the propagation loss difference between the c-Si and a-Si:H waveguides was due to scattering loss from the surface and not material absorption of the a-Si:H. As such, it is reasonable to state that reducing the surface roughness as well as the side wall roughness is very important for fabrication of low-loss a-Si:H waveguides. A summary of the propagation losses for each waveguide is given in Table 2.

Figure 7. Measured and calculated propagation losses as a function of the Si waveguide surface roughness. (Further details about the plotted data are listed in Table 2).

Table 2. Propagation losses of the multilayer a-Si:H waveguides (unit: dB/cm).

| Etching method | 1 <sup>st</sup> layer | 2 <sup>nd</sup> layer |                   | 3 <sup>rd</sup> layer |                   |

|----------------|-----------------------|-----------------------|-------------------|-----------------------|-------------------|

|                | (c-Si)                | Pressure<br>130 Pa    | Pressure<br>30 Pa | Pressure<br>130 Pa    | Pressure<br>30 Pa |

| RIE            | ●6.0                  | ▲10.2                 | <b>■</b> 7.0      | ▼12.0                 | -                 |

| ICP-RIE        | <b>●</b> 1.6          | -                     | ■3.8              | -                     | <b>◆</b> 3.7      |

# 3. LAYER-TO-LAYER TRANSMISSION

# 3.1 The grating-assisted layer-to-layer coupler

#### 3.1.1 Device structure and design

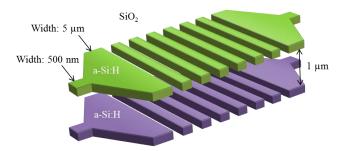

In this section we discuss the implementation of grating couplers to couple light between a single-mode fiber and a photonic waveguide <sup>24,25</sup>. Figure 8 shows the proposed structure of the layer-to-layer grating coupler. This grating structure has been proposed for layer-to-layer coupling in 3D optical circuits <sup>26</sup> in order to couple light with a distance of a few µm between multilayer waveguides (much longer than a vertical directional coupler).

Figure 8. Device structure of the layer-to-layer grating coupler.

500 nm wide a-Si:H wire waveguides were used as the input and output ports for the grating couplers that expanded to 5  $\mu$ m wide waveguides at the grating region in order to mitigate alignment mismatch. A linearly tapered  $200~\mu$ m long structure was employed along this area to avoid reflection and to excite only the fundamental mode in the 5  $\mu$ m

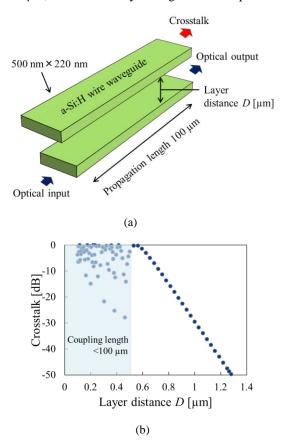

waveguides. The grating depth was fixed at 220 nm (the same thickness as the a-Si:H layer) to simplify the fabrication process by forming the waveguides and gratings in a single step. Furthermore, the distance between layers was set as 1 µm in order to avoid crosstalk in the areas outside of the coupler. (The relationship between layer distance and crosstalk will be discussed later in section 3.2.)

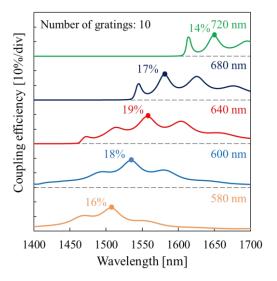

In order to optimize the coupling efficiency of the gratings, a 3D finite-difference time-domain (FDTD) calculation was performed. The grating period is determined by the diffraction wavelength, and the number of grating periods affects the coupling efficiency. TE polarized light was used as the light source where the refractive indices of a-Si:H and  $SiO_2$  were 3.48 and 1.45, respectively. To reduce the calculation time, the Si substrate and air cladding were not included in the simulated area. In the simulation, the grating periods and the number of the grating pairs were varied in the range of 580-720 nm (duty cycle = 50%) and 3-13, respectively. The calculated coupling efficiency as a function of the wavelength for 10 pairs of gratings (with various grating periods) is shown in Fig. 9.

Figure 9. Wavelength dependence of the calculated coupling efficiency for various grating periods.

As can be seen from Fig. 9, the coupling efficiency varied with the grating period, reaching a maximum coupling efficiency of 19% at a wavelength of 1.55  $\mu$ m for a grating period of 640 nm. A red shift of the spectral peak position was observed for longer grating periods as well as several peak positions that can be explained by resonance between the full-etched gratings. This resonance can be suppressed by changing the etching depth.

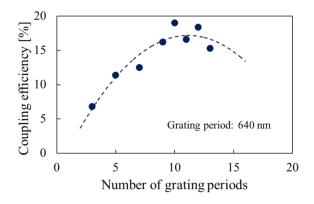

Figure 10. The coupling efficiency dependence on the number of grating periods (grating pairs).

The coupling efficiency at a wavelength of  $1.55~\mu m$  is plotted as a function of the number of grating pairs in Fig. 10. The coupling efficiency peaked at 10 grating pairs after which a lower coupling efficiency was observed due to the light input being first coupled to another layer and then re-radiated by the gratings. In this way the coupling efficiency behaves like a sinusoidal curve.

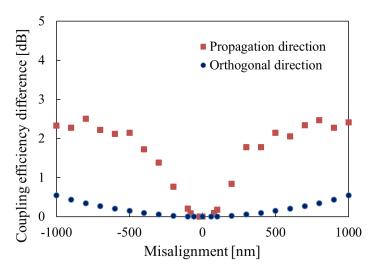

Figure 11. Impact of the misalignment on the coupling efficiency in the propagation direction (squares) and the orthogonal direction (circles).

The tolerance of the grating coupler to fabrication misalignment between the upper and lower gratings was also studied along the directions parallel and orthogonal to the light propagation. The change in the coupling efficiency due to misalignment is plotted in Fig. 11, where the square and circle symbols correspond to differences caused by misalignment in the propagation direction and the orthogonal direction, respectively. In the orthogonal direction the coupling efficiency differed by less than 1 dB even with a misalignment of up to 1  $\mu$ m; this is a result of the widened waveguide width at the grating region. In the propagation direction, the coupling efficiency differed by up to 2.3 dB for a misalignment of 1  $\mu$ m. To maintain a degradation of less than 1 dB the misalignment should be kept below 300 nm. A possible improvement in the misalignment tolerance could be achieved by introducing shallow etched gratings due to the increased number of optimized gratings.

# 3.1.2 Fabrication and measurement

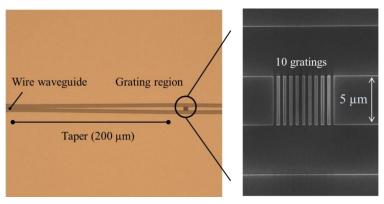

Device fabrication was carried out as follows. Films of 100 nm thick SiO<sub>2</sub> and 220 nm thick a-Si:H were deposited by PECVD on a Si substrate covered with a 3 µm thick thermally oxidized SiO<sub>2</sub> layer. Alignment marks for EB lithography were formed by evaporating Ti/Au film on the 1<sup>st</sup> a-Si:H layer. The waveguides and grating patterns of the above-mentioned structure were formed using ICP-RIE. To act as an over-cladding layer, a 1 µm thick layer of SiO<sub>2</sub> was deposited and flattened by a chemical and mechanical polishing (CMP) process. For the 2<sup>nd</sup> layer, a 220 nm thick a-Si:H layer was deposited and patterned in a similar manner. After covering the 2<sup>nd</sup> a-Si:H layer with SiO<sub>2</sub>, the surface was flattened again by CMP. Optical microscopy and SEM images of the fabricated device are shown in Fig. 12.

Figure 12. Planar view of the fabricated device: Optical microscope image (left) and enlarged SEM image of the gratings (right).

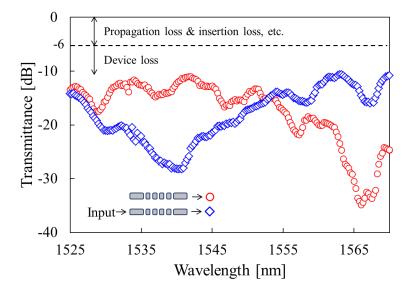

Figure 13. Measured transmittance of the fabricated device (grating period = 640 nm, number of grating pairs = 10).

The coupling efficiency of the grating couplers was measured using TE-polarized light from a tunable laser and the resultant transmittance spectra are shown in Fig 13. The transmitted power between the 1<sup>st</sup> and 2<sup>nd</sup> layer is plotted as open circles and the transmitted power that passes through the gratings of the 2<sup>nd</sup> layer (which was not coupled to the 1<sup>st</sup> layer) is plotted as open diamonds. For the device measured, the grating period was 640 nm and the number of grating pairs was 10, as designed by 3D-FDTD. The total loss, including the propagation and coupling loss (from the fiber to the waveguides), was 6 dB. Accordingly, the coupling efficiency of the fabricated layer-to-layer grating coupler was estimated to be 22% (corresponding to a loss of 6.5 dB). In the current symmetric structure with fully-etched gratings, the light radiated power towards the upward and downward directions should be equal meaning that more than half of the light was wasted for each grating coupler. As such, the maximum coupling efficiency that can be achieved by the paired grating coupler is 25%. Further improvement in the coupling efficiency can be expected by introducing reflectors into the gratings.

#### 3.2 Discussion: Layer distance and crosstalk

In order to realize 3D optical circuits, vertical coupling between layers is necessary. A simple way to achieve this in multilayer waveguides is by using a vertical-stacked directional coupler. There has been a report of a vertical directional coupler with a layer distance of 200 nm<sup>27</sup>, however, in the case of multi-layered optical circuits crosstalk between layers should be considered. Furuya *et al.* reported on a numerical analysis of crosstalk at overpass crossings concluding that the distance between waveguides should be at least 400 nm in order to eliminate mutual coupling <sup>28</sup>. Furthermore, when two vertically stacked waveguides propagate in the same direction, as shown in Fig. 14 (a), optical coupling between the two waveguides occurs in the same way as the directional coupler. In the case of multi-layered optical circuits this optical coupling becomes crosstalk. Fig.14 (b) shows the crosstalk as a function of the layer distance when two vertically stacked waveguides propagate for 100 μm, as calculated by the eigen-mode-expansion method.

Figure 14. (a) Vertically stacked waveguides propagate in the same direction. (b) Optical crosstalk as a function of the layer distance D, for a propagation length of 100  $\mu m$ .

Like the directional coupler, the effective coupling length increases with a longer layer distance. A crosstalk of 0 dB indicates that the whole optical power was transferred to the other waveguide. When the coupling length is shorter than 100  $\mu m$  - which corresponds to the <500 nm layer distance condition of Furuya et~al. - the whole optical power transfers to the other waveguide several times. When the coupling length is longer than 100  $\mu m$  (i.e., the layer distance is greater than 500 nm), the crosstalk decreases with increasing layer distance. In order to achieve a crosstalk of -30dB, the layer distance needs to be at least 1  $\mu m$ . Overall; these calculations indicate the feasibility of a grating type layer-to-layer coupler which is therefore suitable for 3D optical circuits.

# 4. CONCLUSION

For the realization of multi-layered optical circuits for 3D optical interconnects, two basic studies were performed. First, the preparation of multi-layered a-Si:H waveguides was discussed, and their characteristics were investigated. The propagation loss of the 1<sup>st</sup> layer of c-Si, and the 2<sup>nd</sup> and 3<sup>rd</sup> layers of a-Si:H was 6.0 dB/cm, 10.2 dB/cm and 12.0 dB/cm, respectively. The propagation loss was shown to improve to 1.6 dB/cm, 3.8 dB/cm and 3.7 dB/cm, respectively, by reducing the surface and sidewall roughness.

Secondly, in order to achieve high coupling efficiencies as well as high optical isolation between multilayer waveguides, we proposed and demonstrated a layer-to-layer grating coupler with a layer distance of 1 µm. For this configuration a coupling efficiency of 22% was achieved for a grating period of 640 nm and 10 pairs of gratings.

# ACKNOWLEDGMENTS

This research was supported by the Ministry of Education, Culture, Sports, Science and Technology (MEXT); JSPS KAKENHI Grant Numbers 24246061, 22360138, 21226010 and 11J08863; JSPS and the Council for Science and Technology Policy (CSTP) under the Funding program for World-Leading Innovative R&D in Science and Technology (FIRST); and by the Ministry of Internal Affairs and Communications under the Strategic Information and Communications R&D Promotion Programme (SCOPE). The authors thank Minebea Co., Ltd. For help with the ellipsometry measurements of the a-Si:H films presented in this work.

# REFERENCES

- [1] D. A. B. Miller, "Rationale and challenges for optical interconnects to electronic chips," Proc. IEEE 88, 728–749 (2000).

- [2] E. Mohammed, A. Alduino, T. Thomas, H. Braunisch, D. Lu, J. Heck, A. Liu, I. Young, B. Barnett, G. Vandentop and R. Mooney, "Optical interconnect system integration for ultra-short-reach applications," Intel Technol. J. 8, 115–128 (2004).

- [3] D. A. B. Miller, "Device requirements for optical interconnects to silicon chips," Proc. IEEE 97, 1166–1185 (2009).

- [4] G. Chen, H. Chen, M. Haurylau, N. A. Nelson, D. H. Albonesi, P. M. Fauchet and E. G. Friedman, "Predictions of CMOS compatible on-chip optical interconnect," Integration VLSI J. 40, 434–446 (2007).

- [5] T. Tsuchizawa, K. Yamada, T. Watanabe, S. Park, H. Nishi, R. Kou, H. Shinojima and S. -I. Itabashi, "Monolithic integration of Silicon-, Germanium-, and Silica-based optical devices for telecommunications applications," IEEE J. Sel. Top. Quantum Electron. 17, 516–525 (2011).

- [6] R. Soref, "The past, present, and future of silicon photonics," IEEE J. Sel. Top. Quantum Electron. 12, 1678–1687 (2006).

- [7] T. Maruyama, T. Okumura, S. Sakamoto, K. Miura, Y. Nishimoto and S. Arai, "GaInAsP/InP membrane BH-DFB lasers directly bonded on SOI substrate," Opt. Express 14, 8184–8188 (2006).

- [8] Y. Atsumi, M. Oda, J. Kang, N. Nishiyama and S. Arai, "Athermal wavelength filters toward optical interconnection to LSIs," IEICE Trans. Electron. E95-C, 229–236 (2012).

- [9] Y. Vlasov, W. M. J. Green and F. Xia, "High-throughput silicon nanophotonic wavelength-insensitive switch for on-chip optical networks," Nat. Photonics 2, 242–246 (2008).

- [10] P. De. Dobbelaere, A. Narasimha, A. Mekis, B. Welch, C. Bradbury, C. Sohn, D. Song, D. Foltz, D. Guckenberger, G. Masini, J. Schramm, J. White, J. Redman, K. Yokoyama, M. Harrison, M. Peterson, M. Mack, M. Sharp, R. Leblanc, S. Abdalla, S. Gloeckner, S. Hovey, S. Jackson, S. Sahni, S. Yu, T. Pinguet and Y. Liang, "Silicon photonics for high data rate optical interconnect," Proc. IEEE Int. Conf. Optical Interconnects Conference WA2, 113-114 (2012).

- [11] Y. Urino, T. Horikawa, T. Nakamura and Y. Arakawa, "Photonics-electronics convergence system for high density inter-chip interconnects by using silicon photonics," Proc. IEEE Int. Symp. Compound Semiconductor IC Symposium 978-1-4673-0929-5, 1-4 (2012).

Proc. of SPIE Vol. 8630 863008-11

- [12] G. Cocorullo, F. G. D. Corte, R. De Rosa, I. Rendina, A. Rubino and E. Terzini, "Amorphous Silicon-Based Guided-Wave Passive and Active Devices for Silicon Integrated Optoelectronics," IEEE J. Sel. Top. Quantum Electron. 4, 997–1002 (1998).

- [13] A. Biberman, N. Sherwood-Droz, X. Zhu, K. Preston, G. Hendry, J. S. Levy, J. Chan, H. Wang, M. Lipson and K. Bergman, "Photonic network-on-chip architecture using 3D integration," Proc. SPIE 7942, 79420M (2011).

- [14] A. Harke, M. Krause and J. Mueller, "Low-loss singlemode amorphous silicon waveguides," Electron. Lett. 41, 1377–1379 (2005).

- [15] S. K. Selvaraja, E. Sleeckx, M. Schaekers, W. Bogaerts, D. V. Thourhout, P. Dumon and R. Baets, "Low-loss amorphous silicon-on-insulator technology for photonic integrated circuitry," Opt. Commun. 282, 1767–1770 (2009).

- [16] A. Harke, "Amorphous Silicon for the Application in Integrated Optics," Ph. D. Thesis, TU Hamburg-Harburg, Hamburg, Germany, (2010).

- [17] W. Bogaerts, P. Dumon, D. V. Thourhout and R. Baets, "Low-loss, low-cross-talk crossings for silicon-on-insulator nanophotonic waveguides," Opt. Lett. 32, 2801–2803 (2007).

- [18] J. Kang, Y. Atsumi, M. Oda, T. Amemiya, N. Nishiyama and S. Arai, "Low-loss amorphous silicon multilayer waveguides vertically stacked on silicon-on-insulator substrate," Jpn. J. Appl. Phys. 50, 120208 (2011).

- [19] K. Inoue, D. Plumwongrot, N. Nishiyama, S. Sakamoto, H. Enomoto, S. Tamura, T. Maruyama and S. Arai, "Loss reduction of Si wire waveguide fabricated by edge-enhanced writing for electron beam lithography and reactive ion etching using double layered resist mask with C<sub>60</sub>," Jpn. J. Appl. Phys. 48, 030208 (2009).

- [20] I. Adesida, C. Youtsey, A. T. Ping, F. Khan, L. T. Romano and G. Bulman, "Dry and wet etching for group III nitrides," MRS Internet J. Nitride Semicond. Res. 4S1, G1.4 (1999).

- [21] H. Yamada, T. Chu, S. Ishida and Y. Arakawa, "Si photonic wire waveguide devices," IEEE J. Sel. Top. Quantum Electron. 12, 1371–1379 (2006).

- [22] P. K. Tien, "Light waves in thin films and integrated optics," Appl. Opt., 10, 2395-2413 (1971).

- [23]F. P. Pyne and J. P. R. Lancey, "A theoretical analysis of scattering loss from planar optical waveguides," Opt. and Quantum Electron. 26, 977–986 (1994).

- [24] F. Van Laere, T. Claes, J. Schrauwen, S. Scheerlinck, W. Bogaerts, D. Taillaert, L. O'Faolain, D. Van Thourhout and R. Baets, "Compact focusing grating couplers for silicon-on-insulator integrated circuits," IEEE Photon. Technol. Lett. 19, 1919–1921 (2007).

- [25] L. Liu, M. Pu, K. Yvind and J. M. Hvam, "High-efficiency, large-bandwidth silicon-on-insulator grating coupler based on a fully-etched photonic crystal structure," Appl. Phys. Lett. 96, 051126 (2010).

- [26] J. Kang, Y. Atsumi, M. Oda, T. Amemiya, N. Nishiyama and S. Arai, "Layer-to-Layer grating coupler based on hydrogenated amorphous silicon for three-dimensional optical circuits," Jpn. J. Appl. Phys. 51, 120203 (2012).

- [27] R. Sun, M. Beals, A. Pomerene, J. Cheng, C. Hong, L. Kimerling and J. Michel, "Impedance matching vertical optical waveguide couplers for dense high index contrast circuits," Opt. Express 16, 11682–11690 (2008).

- [28] K. Furuya, Y. Sakakibara and M. Mori, "Basic study of coupling on Si waveguides of grade separation by numerical analysis," Proc. 15th Int. Conf. Optoelectronic and Communications Conference 8P-71, 708-709 (2010).